CS基板でLO 4逓倍器を実験しました。

ドレークのジャンクと水晶が見つかったので試しました。

昔のものでIFを1295Mで使っていたものです。

今回は電源三端子なしのユニットです。

外部から8Vを加えて3端子の入出力を短絡しました。

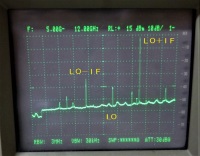

まず4逓倍後の信号をSGから加えて出力が最大になる様にトリミング。

BPFはコの字のライン片側だけ3か所2mm位足しました。

18db位ゲインが取れました。

次に初段のゲートバイアスラインをカットして68μH追加、コイル8mm位と2Pトリマー追加

ドレークの出力を接続して出力が最大になる様にトリマーを調整。

3dbm程度出て来ました。

スプリアスも結構抑えられています。

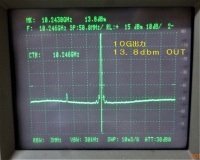

今までのユニットを繋いでIFはSGから5dbm程度入れました。

20mW程度を確認、スプリアスも簡単な外部BPFで取れる程度で実用に成るようです。

ここまで来たら受信コンバーターも試したく成りました。

LOの切り替えはリレーを使わず4逓倍後の余っているFET回路を使って受信時電圧を掛けると

スプリアスは多いが取り出せるかも知れません。

イメージ信号の受信が考えられますが・・・

JA3CVF/日高郡 森本 |

10G出力LO逓倍器付き

出力スプリアス |

10G出力 LO逓倍器付き |

10Gトランスバーター

途中 |

4逓倍スプリアス |

4逓倍器 |

|

|

|